Build breakthrough solutions for AI defect classification for semiconductor wafer/die images.

Grand Finale at IESA Vision Summit 2026 (Bengaluru) — pitch to IESA

leadership + top industry experts.

Build breakthrough solutions for AI defect classification for semiconductor wafer/die images. Grand Finale at IESA Vision Summit 2026 (Bengaluru) — pitch to IESA leadership + top industry experts.

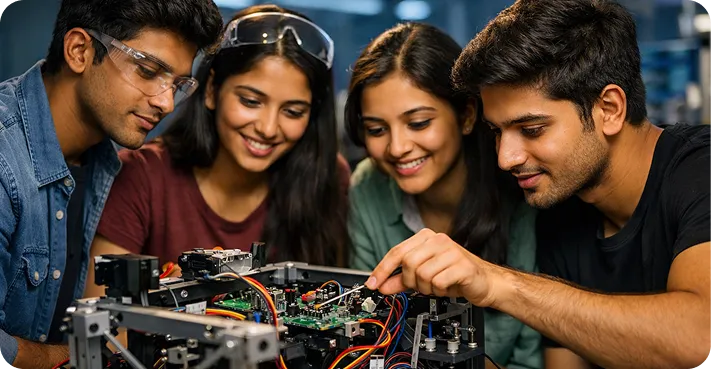

The DeepTech Hackathon is a national platform for building practical, industry-ready solutions in two of the most critical technology domains shaping India’s electronics future: semiconductor design and embedded systems.

This hackathon is designed to do more than just collect ideas. It is structured to help teams move from a problem statement to a clear solution architecture, working prototype/demo, and a compelling pitch, supported by domain mentorship and a transparent evaluation framework.

Participants will explore how AI can enhance core chip design workflows, improving performance, reducing design cycles, and enabling smarter decision-making in areas such as RTL development, verification, design-space exploration, and physical design.

Participants will explore how AI can enhance core chip design workflows, improving performance, reducing design cycles, and enabling smarter decision-making in areas such as RTL development, verification, design-space exploration, and physical design.

Participants will build functional embedded applications on development boards, focusing on real-world use cases such as smart sensing networks, secure gateways, RTOS-based control systems, edge AI prototypes, robotics, and industrial IoT.

The most promising teams will be shortlisted to pitch at the IESA Vision Summit 2026. Finalists will get the opportunity to present to IESA leadership, semiconductor and electronics industry experts, and ecosystem partners offering high visibility, strong credibility, and real opportunities to take solutions forward.

| Team ID - Team Name | Rank | College |

|---|---|---|

| 275 - VisionX | 1st | Chennai Institute of Technology |

| 512 - TRIT | 2nd | Ramco Institute of Technology |

| 991 - Niriksh | 3rd | Indian Institute of Information Technology Indore |

India’s electronics and semiconductor ecosystem is entering a high-growth phase, and the skills demand is shifting fast from “only coding” to deep-tech building across silicon + embedded systems. Chip design complexity is rising, and companies worldwide are increasingly adopting AI/ML inside EDA workflows to improve productivity in areas like verification, PPA optimization, and design-space exploration. At the same time, real products are being built and deployed at the edge (devices, gateways, industrial IoT), where low-latency, secure, reliable embedded applications matter. This hackathon directly aligns with these trends by creating a national platform for talent to build industry-relevant prototypes in two future-critical tracks AI-enabled chip design and embedded development on boards and culminates in a high-value opportunity: finalists pitch at IESA Vision Summit 2026, Bengaluru, in front of IESA leadership and senior industry experts, turning hackathon work into real ecosystem visibility and next-step opportunities.

Builds talent for AI + EDA and embedded/edge two of the fastest-growing deep-tech skill areas.

Moves teams beyond ideas to working demos + measurable outcomes (benchmarks, results, documentation).

Moves teams beyond ideas to working demos + measurable outcomes (benchmarks, results, documentation).

Offers a unique advantage Vision Summit stage access for finalists to pitch and network with the ecosystem.

Semiconductor fabrication involves hundreds of tightly controlled steps. Any step can

introduce microscopic defects that impact performance or cause catastrophic failures. Modern

lines generate terabytes of inspection images daily, captured using tools such as optical

microscopes, Scanning Electron Microscope (SEM), Atomic Force Microscope (AFM), and defect

review stations.

Centralized analysis/manual review struggles due to:

Semiconductor manufacturing produces large volumes of wafer and die inspection

images. Defects in these images can reduce yield and cause failures, but traditional

centralized/manual inspection creates latency, bandwidth bottlenecks, and high infrastructure cost,

making it difficult to scale to real-time production needs.

Your task is to build an Edge-AI capable system that can detect and classify defects in

semiconductor wafer/die images using AI/ML, while balancing accuracy, latency, and compute

efficiency to reflect real fab constraints.

Design and build an Edge-AI powered defect classification system capable of:

Teams must submit the following (as applicable by phase):

Evaluation Data Rule: After the phase-1 submission deadline, the submitted model becomes the

reference model, and no re-submission is allowed. Teams then proceed to next steps and edge-

porting.

| Phase | Phase 1 | Phase 2 | Phase 3 |

|---|---|---|---|

| Who participates | All teams | Shortlisted teams for Phase 2 (30 Teams) | Finalists (10 Teams) |

| Goal | Register and submit the first version of the solution and approach | Validate model generalization using organizer-provided test images | Demonstrate edge readiness and deliver final pitch |

| What teams must submit (Deliverables) | Items #1–5 of deliverables mentioned above | Item #6 of deliverables mentioned above | Items #7–9 of deliverables mentioned above |

| Evaluation Criteria | 1) Dataset quality, dataset size, class balance, model accuracy, model size. 2) A Minimum of 500 images (Clean + Defective) | Prediction accuracy, number of defect classes the model can classify, model size | Successful generation of bitfile, size of generated model stack, patentable concepts, innovation, publication possibility, methodology |

| Steps | 1) Data collection and dataset creation, proposed methodology 2) AI/ML model development | 1) Prediction using hackathon-supplied test dataset | 1) Model porting and optimization for Edge-AI 2) Presentation and documentation |

Team registrations go live. Create your team and complete registration early so you’re ready when problem statements are revealed.

Official problem statements are published. Review problem statement and start planning your approach..

Join the official orientation to understand the problem statement, objective and delivery, hackathon flow, submission format, evaluation criteria, and tips to build a strong entry.

Join quick interactive webinars to understand the concept and get clarification on doubts.

Join quick interactive webinars to understand the concept and get clarification on doubts.

Final deadline for Phase 1 idea submission. Make sure your entry follows the template and is complete.

Selected teams for Phase 2 will be announced on email/portal. Next-step instructions and Phase 2 requirements will be shared..

Mandatory online session for Phase 2 teams realted to deliverables & expectations..

Submit Phase 2 deliverables.Final deadline for Phase 2 submissions. No changes accepted after this.

Finalists are announced and onboarded for the Vision Summit Grand Finale. Travel and venue instructions will be shared.

Focused mentoring to polish the solution, strengthen demo readiness, and finalize the pitch deck.

Focused mentoring to polish the solution, strengthen demo readiness, and finalize the pitch deck.

Finalists pitch on the Vision Summit stage to IESA leadership and senior industry experts. Winners are announced with prizes and next-stage opportunities.

Celebrate brilliance and innovation with exceptional prizes and prestigious recognition!

Total Prize Pool: ₹2,00,000

Finalists get the opportunity to attend the summit and pitch on a high-visibility stage in front of IESA leadership and senior industry experts.

Exclusive hardware / development kits, tool credits, and goodies from sponsoring partners (subject to sponsor availability).

Certificates, digital badges, and feature highlights across IESA + i4C channels for top teams.

Direct networking with industry leaders, semiconductor & embedded experts, startups, and ecosystem partners at the summit.

Top teams get visibility for internships, hiring opportunities, and project collaborations with participating companies and partners.

Director

Design Enablement | AI | Digital Transformation - NXP Semiconductors

Mallikarjuna Bande is a semiconductor leader with 30+ years’ experience driving AI-enabled VLSI innovation.

Director

GlobalFoundries

Jay Shah, with extensive experience in semiconductor engineering focuses on semiconductor device design and characterization

Design Engineer at NXP Semiconductors

Reshma has 8 years experience, Masters from BITS Pilani, works at NXP designing 16nm libraries.

Principal CFM Defect Engineer

GlobalFoundries

She specializes in defect analysis, fault monitoring, and semiconductor yield improvement

Member of Technical Staff

GlobalFoundries

Safeer Afaque specializes in semiconductor automation, analytics, and AI-driven yield engineering.

Sr Business Automation Manager

CTO | Digital Transformation NXP Semiconductors

Amit Dad is a Business leader with 22 + years of experience in Automation

DFT Lead

Qualification | Design Enablement NXP Semiconductors

Avinash Kumar is a DFT engineer with 5 years of experience in DFT qualification, and enablement.

Defects Engineer

GlobalFoundries

He specializes in identifying yield-killing defects and root cause analysis in semiconductor manufacturing.

Head – Research & Innovation

Neilsoft | Secretary, i4C

A technology leader with 22+ years of expertise in software development, specializing in embedded systems and web applications.

Founder & CEO

10cTechClub

Startup entrepreneur and educator with 25+ years experience, founder of 10xTechClub delivering experiential learning.

Lead Subject Matter Expert

L&T EduTech

A passionate educator with 30+ years’ experience in engineering education, specializing in curriculum design, pedagogy, evaluation, and technologies.

Head - Embedded Systems

Aeron Systems Pvt. Ltd.

Bharat Kokate, Head of Embedded Systems and scrum Master, brings 17+ years’ expertise, mentoring innovation through hackathons.

India Electronics and Semiconductor Association (IESA) is India’s leading industry body for ESDM, semiconductors, and intelligent electronics, connecting industry, startups, academia, and policymakers to strengthen India’s innovation and manufacturing ecosystem.

IESA Vision Summit 2026 is IESA’s flagship industry gathering focused on advancing India’s semiconductor and electronics (ESDM) ecosystem bringing together industry leaders, policymakers, startups, academia, and technology experts for strategic discussions, partnerships, and showcases. The 2026 theme is “Design to Manufacturing — Synergy of Product, Production and Skill”, emphasizing India’s transition toward a Product Nation, Production Nation, and Skills Nation.

Delegates

Exhibitors

Keynotes

Panel Discussions

Sessions

Students can register their Teams directly. One student from the team who is the Team leader must register & choose the designation as Team leader as mentioned on the portal and the team members.

Students from any stream, Btech, BE, BCA, MCA, PhD, Etc.

2–4 members (recommended).

Development is online; Grand Finale at IESA Vision Summit 2026, Bengaluru.

Deck + demo/prototype + documentation + repo/video (as applicable).

For embedded track, teams may use their own dev boards and hardware.

Innovation, feasibility, technical depth, impact, demo quality.

Max 10-12 teams will make it to the grand finale.

All updates related to the hackathon will be given on the website itself and email will be sent for ease of communication. We would recommend regularly following the i4C website, to avoid inadvertently missing any emails. Please add support@i4c.into avoid emails from us going into your Spam / Junk folder.

Get all the details about the hackathon, including problem statements, timelines, prize information & FAQ.

Click below to download reference idea submission template.

Click below to know problem statements in more details.

Click below to know how to register for the hackathon.

Scan this QR code using WhatsApp camera to join this group

Our Expert will connect with you shortly!

Our Expert will connect with you shortly!